UG student Ali Hammoud to present his winning Code-a-Chip design at ISSCC 2023

Ali Hammoud, a second-year student in computer engineering, is a winner in the inaugural international Code-a-Chip competition. He will present his project in open-source chip design at the 2023 International Solid-State Circuits Conference (ISSCC), along with 6 other design teams from around the world. His design is called OpenFASoC: Digital LDO Generator.

Hammoud’s design is based on the open-source tool called OpenFASoC, short for Open-Source Fully Autonomous System-on-Chip, which was co-developed by his faculty advisor on the project, Dr. Mehdi Saligane. OpenFASoC was developed for analog circuit design, which is more difficult to automate than digital circuit design.

“Open source chip design reflects the new shift towards hybrid engineers that are in tune with both software and hardware,” said Hammoud. “So I can spend a week designing, or if I’m in tune with software, I can just spend a day coding my chip.”

Hammoud developed a way to autonomously generate a Digital Low Dropout Voltage (LDO) Regulator. LDO regulators are very useful in many applications where stable, regulated voltage is required, such as powering the microcontrollers used in embedded systems, IoT devices, and other electronic applications. They also ensure efficient power consumption in battery-powered devices, such as mobile phones and other portable electronics.

In addition, Digital LDOs can be used to power analog-to-digital converters (ADCs) and digital-to-analog converters (DACs), which are used in a wide range of applications, including communication systems, instrumentation, and control systems. And they are used to power the RF front-end circuits of wireless devices, such as mobile phones, WiFi routers, and Bluetooth devices.

“With the analog blocks,” explained Hammoud, “we’re using the open source tool called OpenROAD for the digital work,” said Hammoud. “And we’re using our own Python scripts to combine the analog blocks with the digital flow.”

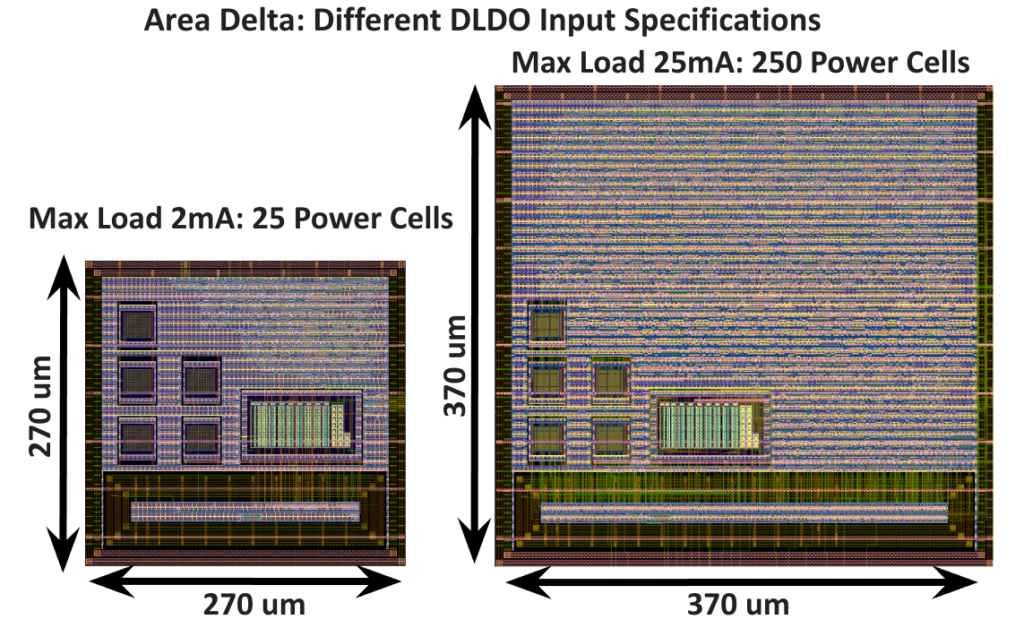

A design engineer provides a capacitor, power cell, and comparator, and then the specifications (ie, load and current) are fed into the LDO generator, which in turn searches the model file, and maps out the needed array size for the PMOS cells.

Shown above are two designs that were automatically generated and optimized based on different inputs.

Hammoud will present his design at ISSCC 2023 both verbally and in a poster session at the Student-Research Preview. In addition to being advised by Saligane, one of the leaders in open-source hardware, he worked with Pranav Lulu, a recent graduate of Vishwakarma Institute of Information Technology.

“This experience has opened my eyes to a lot of opportunities, and avenues I can take,” said Hammoud. “I signed up for a lot of different types of sessions at ISSCC, such as high performance memory, high performance computing, and analog design.”

The Code-a-Chip competition was sponsored by the CHIPS Alliance.

MENU

MENU